自主科技

進軍產業鏈最高端

中美貿易戰發展成科技戰爭,美國禁制中興,再向華為發出禁令。美國是芯片大國,雄踞晶片生產和設計,也擁有芯片設計的核心技術。

2018年,中國的總進口額約為14萬億元人民幣,其中芯片進口達2萬億元,佔全國進口商品額的14%,同期石油進口額1.59億元人民幣,芯片進口急增,比石油更具戰略意義。

中國曾經多次鼓勵國內芯片業發展,中國可自行生產軍用、航天、衛星,甚至超級電腦芯片,也出口低端的芯片;商業高端芯片幾乎全靠入口,據官方統計,中國對於高端芯片的依賴程度,高達八成,比石油業的七成還高。

芯片成為中國的「軟肋」,華為事件剛好打中要害,以致解除華為禁制,成為中美重啟談判的「前設條件」。

有關中國高端芯片,為何躑躅不前,可謂人言人殊。華為有自行設計芯片的海思(HiSilicon),開發出手機的ARM芯片「麒麟」,伺服器的鯤鵬芯片。

不過,美國禁令包括芯片設計軟件Synopsys和Cadence,均是電子設計自動化(EDA)工具包,直接打擊海思業務。EDA是芯片設計仿真和驗證工具,處於半導體產業鏈最上游,最高端的節點上。

有關中國芯片產業鏈,再度受到關注,中國也加快發展EDA產業。香港也有芯片設計科技,獲得頂級芯片設計廠訂單,隨時開拓芯片業一片藍海市場。

高端芯片包含數以十億計晶體,不可能由人工設計,芯片設計離不開EDA工具包。隨着芯片集成愈來愈密集,支援高速運算、低功耗、高性能,沒有可靠性的運算輔助設計工具,不可能完成芯片設計。

全球芯片EDA設計工具競爭慘烈,最後剩下了Synopsys和Cadence兩家美國公司,仍然高速增長,另一家Mentor Graphics被西門子收購後,逐漸失去活力。

美國壟斷EDA

美國壟斷EDA市場;香港科學園的初創奇捷開發的EDA工具,已取得全球排名前五之大晶片設計廠商投資和訂單,本港沒任何芯片生產,卻竟在高端芯片設計大放異彩。

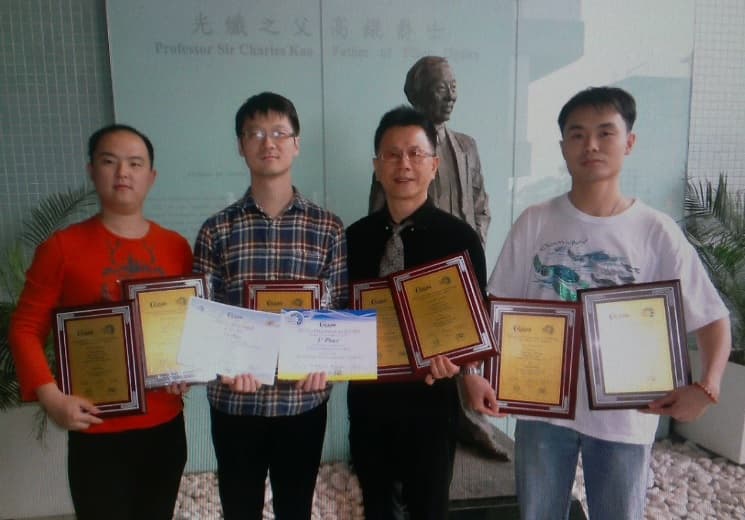

奇捷是數位中文大學工程學院邏輯綜合實驗室研發團隊創建,曾連續三次在Cadence主辦,最高級別ICCAD世界競賽奪冠,破了全球的紀錄,已推出可發現電路錯誤設計,並局部修正功能,避免重新製作電路,縮減設計週期節省成本。另一種產品可以優化電路的時序性能,通過獨特電路局部邏輯重構技術,已經充分優化的電路性能進行進一步提升。

減低設計風險

芯片設計電路後,就會生產光罩(Mask),然後才以光通過帶電路的掩膜,投影到塗有光敏膠的晶圓,原理是利用光刻機光線反射,電路圖複製至感光材料,再用刻蝕機將暴露出來多餘矽片刻蝕掉。經過離子注入複雜工藝,便有了半導體的特性,最後測試,分割,封裝,才完成了芯片。

目前,全球光刻機領先廠商為荷蘭ASML,連日本光刻廠商亦被邊緣化,可見ASML技術優勢;中國光刻技術嚴重落後,ASML暫時無可動搖。

不過,從設計到輸出光罩,設計過程涉及2至4個月,成本也高得驚人,單是設計費用已涉及數百萬美元。光罩成本隨芯片制程改進上升,28nm制程光罩約2至4百萬美元,但低於10nm 光罩總成本以千萬美元計算,必須有極大銷量。這也解釋何以美國壟斷了高端芯片,芯片愈高端銷量愈大,才有足夠經濟規模,承擔高昂的開發成本和風險,後來者難以追上,如果設計過程有誤,損失更加慘重。

EDA是名符其實「深科技」,涉及極難克服的數學難題。芯片從設計到開發光罩,以至製作流片,一旦發現電路有瑕疵,又得重頭做起,損失不菲,EDA修正錯誤能力甚為關鍵。

2013年,吳有亮教授,與數位中大電算系邏輯綜合實驗室博士生,包括了魏星, 林德基, 刁屹,創立奇捷科技並於2015年加入科學園,推出了首款(Functional) Engineering Change Order (ECO),可於集成電路設計末段, 甚至完成光罩後,自動更正設計錯誤或緊急規格修訂,毋須重新設計,避免交期違約風險。

上述產品牽涉到EDA邏輯與物理設計複雜技術,只有兩家EDA設計工具,有能力研發商業級ECO產品,價格極高。目前,全球數家芯片設計廠正試用奇捷科技ECO,已獲韓國三星首爾本部、矽創電子(Sitronix)、ITE、信驊科技(ASPEED)等訂單。

LEC性能冠色全球

有時,電路設計也會在最後一刻進行修改,以合併某些功能、時序、電源或修正,或者包括一些額外邏輯,如掃描邏輯、電源控制等;上述變化也需要驗證。

奇捷科技也具備「邏輯等價性檢查」(Logical equivalence checking)LEC產品:驗證兩個設計在暫存器之間具有相同組合邏輯過程,兩個被比較的設計,也應具有相同數量的暫存器,用於驗證不同抽象等級的設計,優化電路設計。

吳有亮說,奇捷團隊曾經在2014年設計LEC比賽上,榮獲冠軍後仍繼續改進技術終至作到完全解決Cadence 提出之286個案,運算速度比對手,快出3200倍!解決的個案多出2.17倍。

奇捷的科技總監魏星,14歲就獲奧數冠軍。吳有亮說,LEC 涉及數學上最難解決的 NP-完全 題目, 奇捷團隊首次實驗上作到P時全解公開的NP-完全題組,魏星是他中大所遇,最佳的研究生之一,多次在芯片設計揚威;奇捷科技Easy LEC亦已申請專利,即將推出市場。

相較於EDA的巨頭,奇捷科技還只是一家小型團隊,產品線也不完整。中美角力下,中國芯片設計正急起直追。

奇創開發的方案,加大柏克萊分校科研團隊亦到訪取經。加大柏克萊分校也是研究新一代處理器指令集RISC-V重鎮,中國極關注RISC-V 開源指令集,作替代英特爾和ARM專屬架構方案,成立「中國RISC-V產業聯盟」和「中國開放指令生態系統(RISC-V)聯盟」。開源源芯片設計可大大降低設計的門檻,即使3-5人小團隊,3-4個月內以幾萬元,便能研製出一款晶片,中國有300家企業加入了RISC-V基金會,加上政府支持,SoC市場正醞釀巨變。

說不定,有一天EDA市場也會東移。